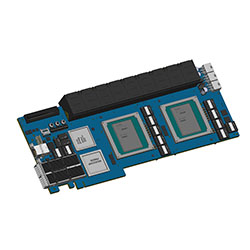

Aldec has introduced the HS-VU19PD-ZU7EV, an ASIC/SoC physical prototype and hardware emulation board that can contain approximately 83M ASIC door design dimensions.

The device uses only two FPGas to provide logic, compared to boards of similar capacity. This simplifies FPGA partitioning and reduces project startup time for medium-sized ASIC or SoC designs. For larger designs, the four boards can be connected via a high-speed backplane, providing the equivalent of about 332M ASIC doors. It can also connect the backplane together (up to three) to fit the design of approximately 996M ASIC doors.

The logic module FPgas of this device are all Virtex UltraScale+ VU19P devices, which are Xilinx fpGas with the highest logical capacity to date. The company's new HES boards also offer the Xilinx Zynq UltraScale+ ZU7EV MPSoC. As a host module, it features ARM Cortex-A53 quad-core, ARM Cortex-R5 dual-core real-time processing unit and PCIe Gen3 embedded IP.

Chris Stinson, senior director of test, measurement and simulation markets at Xilinx said“”"Our newest Virtex UltraScale+ VU19P device is naturally designed for ASIC and SoC prototyping," "These two devices from Aldec, along with our most powerful Zynq fpga, have formed A very versatile platform that allows designers to fast-track their ASIC and SoC projects.”

Zibi Zalewski, General Manager of Aldec hardware commented: "For this new platform, we have replicated most of the system architecture of our popular dual FPGA boards in the HES 7 family, and integrated Xilinx's latest and largest UltraScale+ FPGas into vastly expanding the capacity and functionality of simulation and prototyping scenarios. In addition, our use of Zynq US+ devices as controllers meant that it could host a test platform for prototyping. In fact, our HES board prototyping and simulation capabilities are unique to Aldec."

Zalewski went on to note that revisions to HS-DVM, Aldec's fully automated and scalable hybrid validation environment for SoC and ASIC designs, are planned. "This will further unleash the power of the new board, for example, through enhanced commissioning capabilities," he added.