The ISL6324 dual PWM controller offers high efficiency and tight tuning from two synchronous step-down DC/DC converters. The ISL6324 supports hybrid power control for AMD processors and operates from the 6-bit parallel VID interface (PVI) or serial VID interface (SVI).

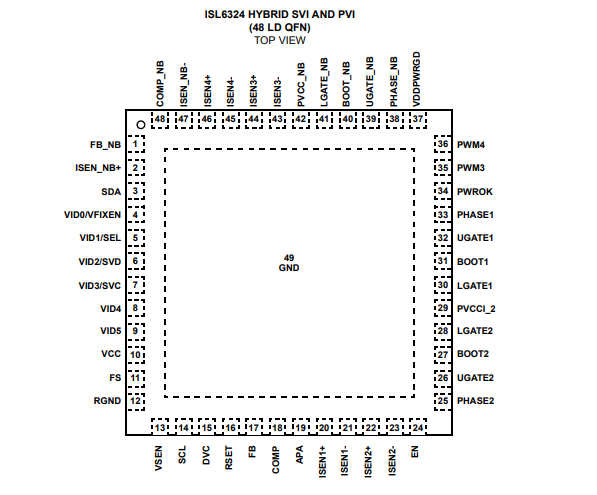

Pinout

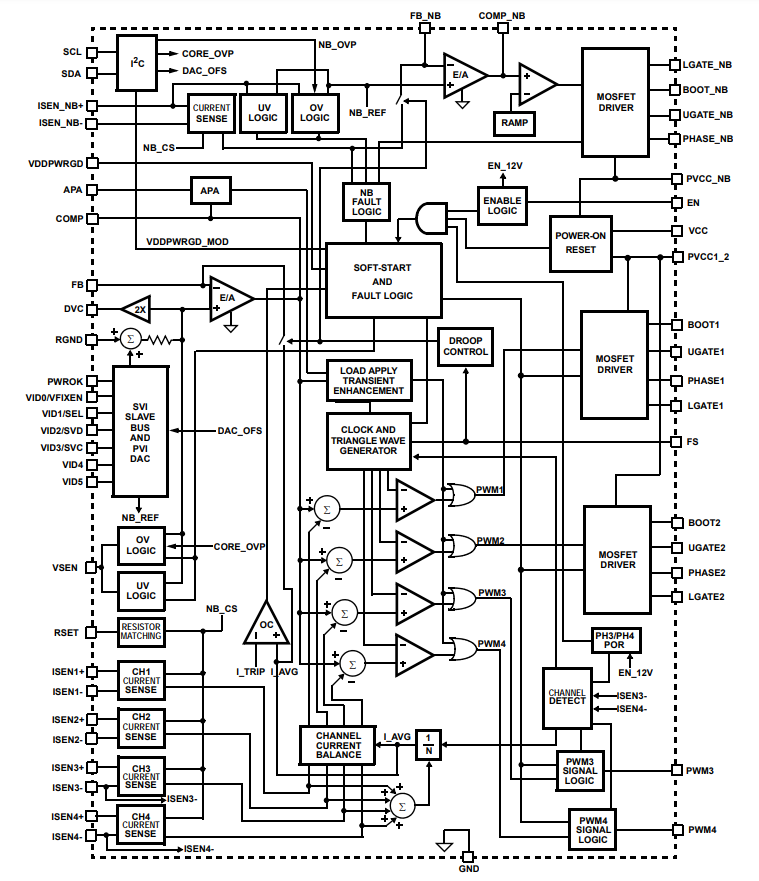

The dual-output ISL6324 features a multiphase controller that supports a single-plane VDD core voltage and a single-phase controller that supports power to the North Bridge (VDDNB) in SVI mode. Only the polyphase controller is active in PVI mode to support processors that only support single-plane VDD. Using 2-4 phase PWM voltage regulator (VR) controller, the precision single plane core voltage regulation system is realized.

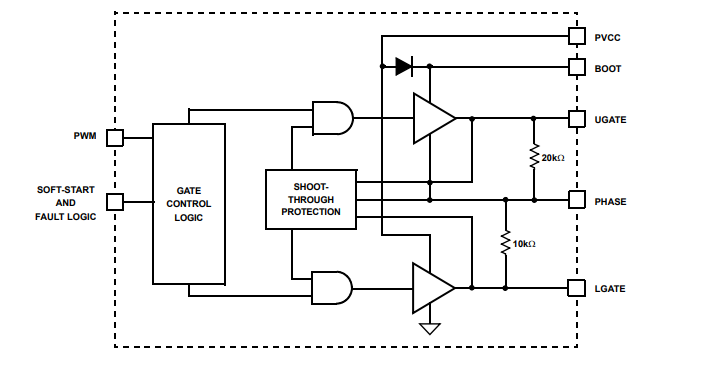

The integration of two power MOSFET drivers increases layout flexibility and reduces the number of external components in the polyphase portion. A single-phase PWM controller with integrated drivers provides a second precision voltage regulation system for the north bridge portion of the processor.

Integrated drive block diagram

This single chip dual controller with integrated drive solution provides a cost - and space-saving power management solution. For applications that benefit from load line programming to reduce bulk output capacitors, the ISL6324 features a drop in output voltage. The multiphase section also includes advanced control loop functionality for load applications and removal for optimal transient response.

One of these features is high precision, fully differential, continuous DCR current sensing for load line programming and channel current balancing. Double edge modulation is another unique feature that allows for faster initial responses to high di/dt load transients. The ISL6324 integrates with the I2C bus ™ to provide independent programmable output voltage offsets for both Core and Northbridge. The I2C bus can also be used to set the PGOOD and OVP levels.

Controller block diagram