|

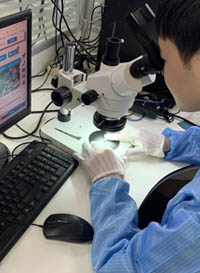

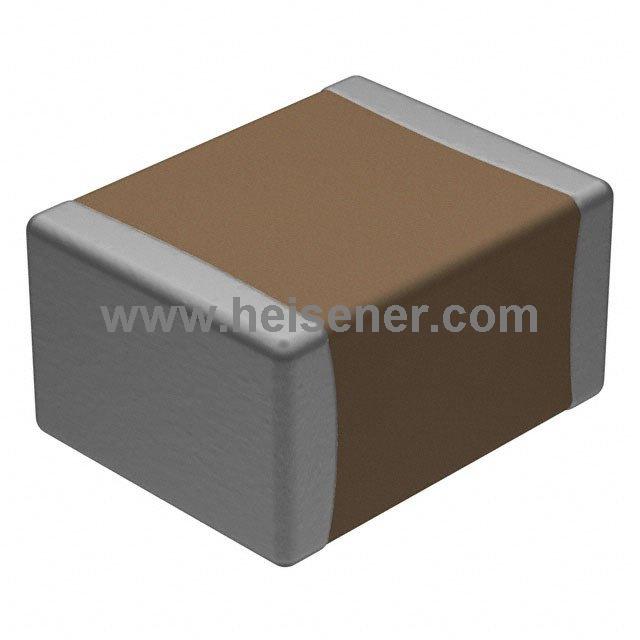

CDR32BP120BFZMAT |

Vishay Vitramon, CAP CER 12PF 100V 1% BP 1206, 1206 (3216 Metric), AVR? ATmega |

View

|

|

VJ1210A120JBCAT4X |

Vishay Vitramon, CAP CER 12PF 200V NP0 1210, 1210 (3225 Metric), AVR? ATmega |

View

|

|

ALD110800APCL |

Advanced Linear Devices Inc., MOSFET 4N-CH 10.6V 16DIP, 16-DIP (0.300", 7.62mm), AVR? ATmega |

View

|

|

KSC815YTA |

Fairchild/ON Semiconductor, TRANS NPN 45V 0.2A TO-92, TO-226-3, TO-92-3 (TO-226AA) (Formed Leads), AVR? ATmega |

View

|

|

SMDJ45A M6G |

TSC America Inc., DIODE, TVS, UNIDIRECTIONAL, 3000, DO-214AB, SMC, AVR? ATmega |

View

|

|

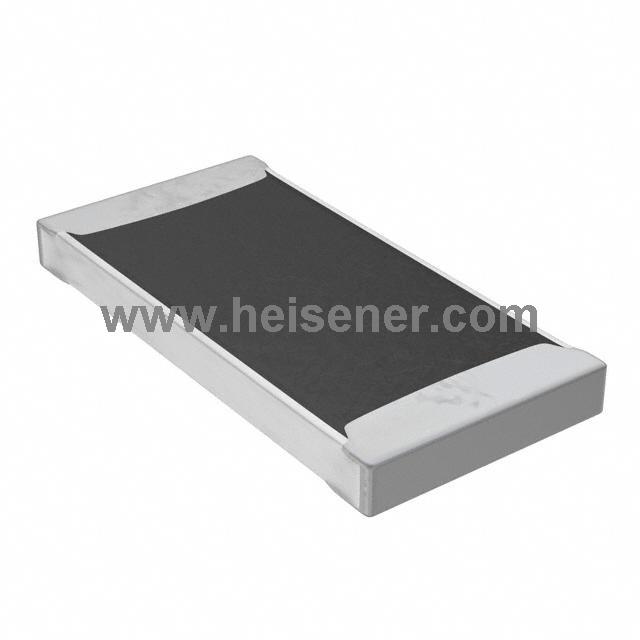

TNPW251236K0BETG |

Vishay Dale, RES SMD 36K OHM 0.1% 1/2W 2512, 2512 (6432 Metric), AVR? ATmega |

View

|

|

RP73D2B93R1BTDF |

TE Connectivity Passive Product, RES SMD 93.1 OHM 0.1% 1/4W 1206, 1206 (3216 Metric), AVR? ATmega |

View

|

|

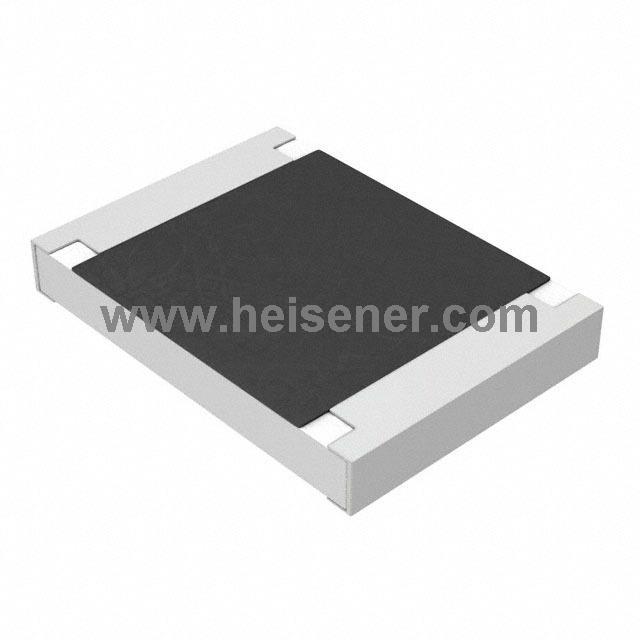

ERJ-S12F5760U |

Panasonic Electronic Components, RES SMD 576 OHM 1% 3/4W 1812, 1812 (4532 Metric), AVR? ATmega |

View

|

|

RG2012N-682-W-T1 |

Susumu, RES SMD 6.8K OHM 0.05% 1/8W 0805, 0805 (2012 Metric), AVR? ATmega |

View

|

|

BCS-101-SM-S-PE-BE |

Samtec Inc., BOX CONNECTOR SOCKET STRIP, -, AVR? ATmega |

View

|

|

5018645090 |

Molex, LLC, CONN FFC BOTTOM 50POS 0.50MM R/A, -, AVR? ATmega |

View

|

|

MS3181-22N |

Amphenol PCD, 26482 D/C RECP SZ 22 CAD OD, -, AVR? ATmega |

View

|